## CMOS SuperSync FIFO™ 32,768 x 18 65,536 x 18

IDT72275 IDT72285

## **FEATURES:**

- Choose among the following memory organizations: IDT72275 — 32,768 x 18

- $ID1/22/5 32,708 \times 18$

- IDT72285 65,536 x 18

- Pin-compatible with the IDT72255LA/72265LA SuperSync FIFOs

- 10ns read/write cycle time (6.5ns access time)

- Fixed, low first word data latency time

- Auto power down minimizes standby power consumption

- Master Reset clears entire FIFO

- Partial Reset clears data, but retains programmable settings

- Retransmit operation with fixed, low first word data latency time

- Empty, Full and Half-Full flags signal FIFO status

- Programmable Almost-Empty and Almost-Full flags, each flag can default to one of two preselected offsets

- Program partial flags by either serial or parallel means

- Select IDT Standard timing (using EF and FF flags) or First Word Fall Through timing (using OR and IR flags)

- Output enable puts data outputs into high impedance state

- Easily expandable in depth and width

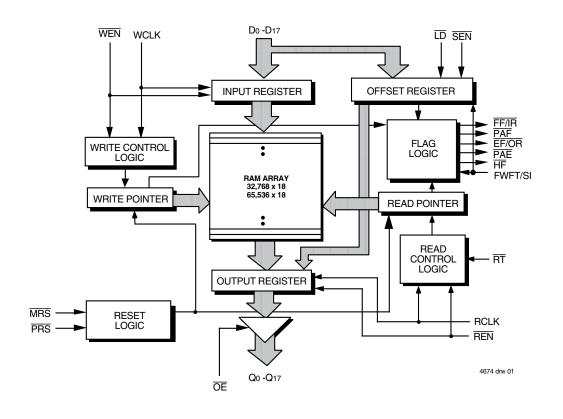

# FUNCTIONAL BLOCK DIAGRAM

- Independent Read and Write Clocks (permit reading and writing simultaneously)

- Available in the 64-pin Thin Quad Flat Pack (TQFP) and the 64pin Slim Thin Quad Flat Pack (STQFP)

- High-performance submicron CMOS technology

- Industrial temperature range (-40°C to +85°C) is available

# **DESCRIPTION:**

The IDT72275/72285 are exceptionally deep, high speed, CMOS First-In-First-Out (FIFO) memories with clocked read and write controls. These FIFOs offer numerous improvements over previous SuperSync FIFOs, including the following:

- The limitation of the frequency of one clock input with respect to the other has been removed. The Frequency Select pin (FS) has been removed, thus it is no longer necessary to select which of the two clock inputs, RCLK or WCLK, is running at the higher frequency.

- The period required by the retransmit operation is now fixed and short.

- The first word data latency period, from the time the first word is written to an empty FIFO to the time it can be read, is now fixed and short. (The variable clock cycle counting delay associated with the latency period found on previous SuperSync devices has been eliminated on this SuperSync family.)

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. The SuperSync FIFO is a trademark of Integrated Device Technology, Inc. The SuperSync FIFO is a trademark of Integrated Device Technology, Inc.

# DESCRIPTION (CONTINUED)

SuperSync FIFOs are particularly appropriate for network, video, telecommunications, data communications and other applications that need to buffer large amounts of data.

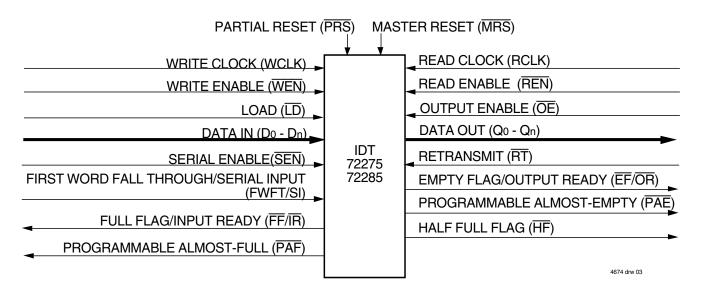

The input port is controlled by a Write Clock (WCLK) input and a Write Enable (WEN) input. Data is written into the FIFO on every rising edge of WCLK when WEN is asserted. The output port is controlled by a Read Clock (RCLK) input and Read Enable (REN) input. Data is read from the FIFO on every rising edge of RCLK when REN is asserted. An Output Enable ( $\overline{OE}$ ) input is provided for three-state control of the outputs.

The frequencies of both the RCLK and the WCLK signals may vary from 0 to fMAX with complete independence. There are no restrictions on the frequency of the one clock input with respect to the other.

There are two possible timing modes of operation with these devices: IDT Standard mode and First Word Fall Through (FWFT) mode.

In *IDT Standard mode*, the first word written to an empty FIFO will not appear on the data output lines unless a specific read operation is performed. A read operation, which consists of activating REN and enabling

arising RCLK edge, will shift the word from internal memory to the data output lines.

In *FWFT mode*, the first word written to an empty FIFO is clocked directly to the data output lines after three transitions of the RCLK signal. A REN does not have to be asserted for accessing the first word. However, subsequent words written to the FIFO do require a LOW on REN for access. The state of the FWFT/SI input during Master Reset determines the timing mode in use.

For applications requiring more data storage capacity than a single FIFO can provide, the FWFT timing mode permits depth expansion by chaining FIFOs in series (i.e. the data outputs of one FIFO are connected to the corresponding data inputs of the next). No external logic is required.

These FIFOs have five flag pins, EF/OR (Empty Flag or Output Ready), FF/IR (Full Flag or Input Ready), HF (Half-full Flag), PAE (Programmable Almost-Empty flag) and PAF (Programmable Almost-Full flag). The EF and FF functions are selected in IDT Standard mode. The IR and OR functions are selected in FWFT mode. HF, PAE and PAF are always available for use, irrespective of timing mode.

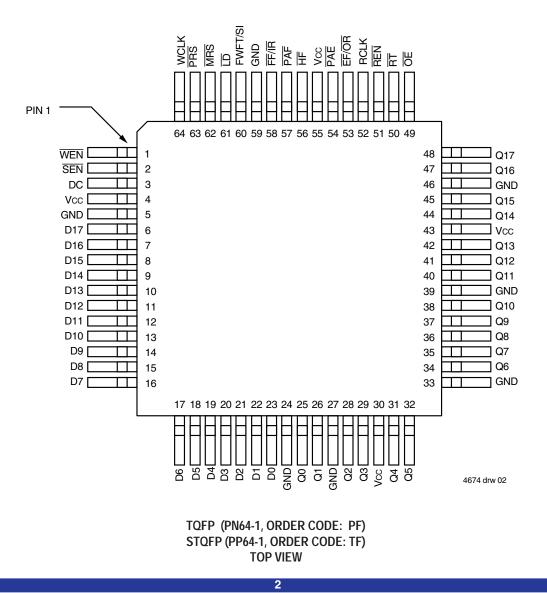

### PIN CONFIGURATIONS

### **DESCRIPTION (CONTINUED)**

PAE and PAF can be programmed independently to switch at any point in memory. (See Table I and Table II.) Programmable offsets determine the flag switching threshold and can be loaded by two methods: parallel or serial. Two default offset settings are also provided, so that PAE can be set to switch at 127 or 1,023 locations from the empty boundary and the PAF threshold can be set at 127 or 1,023 locations from the full boundary. These choices are made with the LD pin during Master Reset.

For serial programming, SEN together with LD on each rising edge of WCLK, are used to load the offset registers via the Serial Input (SI). For parallel programming, WEN together with LD on each rising edge of WCLK, are used to load the offset registers via Dn. REN together with LD on each rising edge of RCLK can be used to read the offsets in parallel from Qn regardless of whether serial or parallel offset loading has been selected.

During Master Reset ( $\overline{\text{MRS}}$ ) the following events occur: The read and write pointers are set to the first location of the FIFO. The FWFT pin selects IDT Standard mode or FWFT mode. The  $\overline{\text{LD}}$  pin selects either a partial flag default setting of 127 with parallel programming or a partial flag default setting

of 1,023 with serial programming. The flags are updated according to the timing mode and default offsets selected.

The Partial Reset (PRS) also sets the read and write pointers to the first location of the memory. However, the timing mode, partial flag programming method, and default or programmed offset settings existing before Partial Reset remain unchanged. The flags are updated according to the timing mode and offsets in effect. PRS is useful for resetting a device in midoperation, when reprogramming partial flags would be undesirable.

The Retransmit function allows data to be reread from the FIFO more than once. A LOW on the  $\overline{\text{RT}}$  input during a rising RCLK edge initiates a retransmit operation by setting the read pointer to the first location of the memory array.

If, at any time, the FIFO is not actively performing an operation, the chip will automatically power down. Once in the power down state, the standby supply current consumption is minimized. Initiating any operation (by activating control inputs) will immediately take the device out of the power down state.

The IDT72275/72285 are fabricated using IDT's high speed submicron CMOS technology.

Figure 1. Block Diagram of Single 32,768 x 18 and 65,536 x 18 Synchronous FIFO

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Rating                                  | Commercial  | Unit |

|--------|-----------------------------------------|-------------|------|

| VTERM  | Terminal Voltage<br>with respect to GND | –0.5 to +7  | V    |

| Tstg   | Storage<br>Temperature                  | -55 to +125 | °C   |

| Ιουτ   | DC Output Current                       | –50 to +50  | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# RECOMMENDED DC OPERATING CONDITIONS

| Symbol             | Parameter                             | Min. | Тур. | Max. | Unit |

|--------------------|---------------------------------------|------|------|------|------|

| Vcc                | Supply Voltage(Com'l & Ind'l)         | 4.5  | 5.0  | 5.5  | V    |

| GND                | Supply Voltage(Com'l & Ind'l)         | 0    | 0    | 0    | V    |

| Vih                | Input High Voltage<br>(Com'I & Ind'I) | 2.0  | _    | _    | v    |

| VIL <sup>(1)</sup> | Input Low Voltage<br>(Com'l & Ind'l)  | _    | _    | 0.8  | V    |

| Та                 | Operating Temperature<br>Commercial   | 0    | -    | +70  | °C   |

| Та                 | Operating Temperature<br>Industrial   | -40  | _    | +85  | °C   |

### NOTE:

1. 1.5V undershoots are allowed for 10ns once per cycle.

# **DC ELECTRICAL CHARACTERISTICS**

(Commercial: VCC =  $5V \pm 10\%$ , TA =  $0^{\circ}$ C to + $70^{\circ}$ C; Industrial: VCC =  $5V \pm 10\%$ , TA =  $-40^{\circ}$ C to + $85^{\circ}$ C)

|                         | IDT72275<br>IDT72285<br>Commercial & Industrial <sup>(1)</sup><br>tclk = 10, 15, 20 ns |      | 2285<br>& Industrial <sup>(1)</sup> |      |

|-------------------------|----------------------------------------------------------------------------------------|------|-------------------------------------|------|

| Symbol                  | Parameter                                                                              | Min. | Max.                                | Unit |

| LI <sup>(2)</sup>       | Input Leakage Current                                                                  | _1   | 1                                   | μA   |

| LO <sup>(3)</sup>       | Output Leakage Current                                                                 | -10  | 10                                  | μA   |

| Vон                     | Output Logic "1" Voltage, IOH = –2 mA                                                  | 2.4  | _                                   | V    |

| Vol                     | Output Logic "0" Voltage, IOL = 8 mA                                                   | _    | 0.4                                 | V    |

| ICC1 <sup>(4,5,6)</sup> | Active Power Supply Current                                                            | _    | 90                                  | mA   |

| ICC2 <sup>(4,7)</sup>   | StandbyCurrent                                                                         | —    | 20                                  | mA   |

NOTES:

1. Industrial temperature range product for 15ns and 20ns speed grade are available as a standard device.

2 .Measurements with 0.4  $\leq$  ViN  $\leq$  Vcc.

3.  $\overline{\text{OE}} \geq$  VIH, 0.4  $\leq$  Vout  $\leq$  Vcc.

4. Tested with outputs open (IOUT = 0).

5. RCLK and WCLK toggle at 20 MHz and data inputs switch at 10 MHz.

6. Typical Icc1 = 20 + 1.8\*fs + 0.02\*CL\*fs (in mA) with Vcc = 5V, ta = 25°C, fs = WCLK frequency = RCLK frequency (in MHz, using TTL levels), data switching at fs/2, CL = capacitive load (in pF).

7. All Inputs = Vcc - 0.2V or GND + 0.2V, except RCLK and WCLK, which toggle at 20 MHz.

## CAPACITANCE

$(TA = +25^{\circ}C, f = 1.0MHz)$

| Symbol                | Parameter <sup>(1)</sup> | Conditions    | Max. | Unit |

|-----------------------|--------------------------|---------------|------|------|

| CIN <sup>(2)</sup>    | Input<br>Capacitance     | $V_{IN} = 0V$ | 10   | pF   |

| Cout <sup>(1,2)</sup> | Output<br>Capacitance    | Vout = 0V     | 10   | pF   |

NOTES:

1. With output deselected, ( $\overline{OE} \ge VIH$ ).

2. Characterized values, not currently tested.

# AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

(Commercial: Vcc =  $5V \pm 10\%$ , TA =  $0^{\circ}$ C to + $70^{\circ}$ C; Industrial: Vcc =  $5V \pm 10\%$ , TA =  $-40^{\circ}$ C to + $85^{\circ}$ C)

|               |                                                  | Commercial  |        | Commercial & Industrial <sup>(2)</sup> |        |             |        |      |

|---------------|--------------------------------------------------|-------------|--------|----------------------------------------|--------|-------------|--------|------|

|               |                                                  | IDT72275L10 |        | IDT72275L15                            |        | IDT72275L20 |        |      |

|               |                                                  | IDT722      | 285L10 | IDT722                                 | 285L15 | IDT722      | 285L20 |      |

| Symbol        | Parameter                                        | Min.        | Max.   | Min.                                   | Max.   | Min.        | Max.   | Unit |

| fs            | Clock Cycle Frequency                            | _           | 100    | —                                      | 66.7   | —           | 50     | MHz  |

| tA            | Data Access Time                                 | 2           | 6.5    | 2                                      | 10     | 2           | 12     | ns   |

| <b>t</b> CLK  | Clock Cycle Time                                 | 10          | _      | 15                                     | _      | 20          | —      | ns   |

| tськн         | Clock High Time                                  | 4.5         | _      | 6                                      | _      | 8           | _      | ns   |

| <b>t</b> CLKL | Clock Low Time                                   | 4.5         | _      | 6                                      | _      | 8           | —      | ns   |

| tDS           | Data Setup Time                                  | 3           | _      | 4                                      | _      | 5           | _      | ns   |

| tDH           | Data Hold Time                                   | 0           | _      | 1                                      | _      | 1           | _      | ns   |

| tens          | Enable Setup Time                                | 3           | _      | 4                                      | _      | 5           | —      | ns   |

| tenh          | Enable Hold Time                                 | 0           | _      | 1                                      | _      | 1           | _      | ns   |

| tlds          | Load Setup Time                                  | 3           | _      | 4                                      | _      | 5           | _      | ns   |

| tldh          | Load Hold Time                                   | 0           | _      | 1                                      | _      | 1           | _      | ns   |

| tRS           | Reset Pulse Width <sup>(3)</sup>                 | 10          | _      | 15                                     | _      | 20          | _      | ns   |

| trss          | Reset Setup Time                                 | 10          | _      | 15                                     | _      | 20          | _      | ns   |

| trsr          | Reset Recovery Time                              | 10          | _      | 15                                     | _      | 20          | _      | ns   |

| trsf          | Reset to Flag and Output Time                    | _           | 10     | _                                      | 15     | _           | 20     | ns   |

| <b>t</b> fwft | Mode Select Time                                 | 0           | _      | 0                                      | _      | 0           | _      | ns   |

| trts          | Retransmit Setup Time                            | 3           | _      | 4                                      | _      | 5           | _      | ns   |

| tolz          | Output Enable to Output in Low Z <sup>(4)</sup>  | 0           | _      | 0                                      | _      | 0           | _      | ns   |

| toe           | Output Enable to Output Valid                    | 2           | 6      | 3                                      | 8      | 3           | 10     | ns   |

| toнz          | Output Enable to Output in High Z <sup>(4)</sup> | 2           | 6      | 3                                      | 8      | 3           | 10     | ns   |

| twff          | Write Clock to FF or IR                          | _           | 6.5    | _                                      | 10     | _           | 12     | ns   |

| <b>t</b> REF  | Read Clock to $\overline{EF}$ or $\overline{OR}$ | _           | 6.5    | _                                      | 10     | _           | 12     | ns   |

| <b>t</b> PAF  | Write Clock to PAF                               | _           | 6.5    | _                                      | 10     | _           | 12     | ns   |

| <b>t</b> PAE  | Read Clock to PAE                                | _           | 6.5    | _                                      | 10     | _           | 12     | ns   |

| thf           | Clock to HF                                      | _           | 16     | _                                      | 20     | _           | 22     | ns   |

| tskew1        | Skew time between RCLK and WCLK for FF/IR        | 5           | _      | 6                                      | _      | 10          | _      | ns   |

| tskew2        | Skew time between RCLK and WCLK for PAE and PAF  | 12          | _      | 15                                     | _      | 20          | _      | ns   |

| tskew3        | Skew time between RCLK and WCLK for EF/OR        | 60          | _      | 60                                     | _      | 60          | _      | ns   |

NOTES:

1. All AC timings apply to both Standard IDT mode and First Word Fall Through mode.

2. Industrial temperature range product fot 15ns and 20ns speed grade are available as a standard device.

3. Pulse widths less than minimum values are not allowed.

4. Values guaranteed by design, not currently tested.

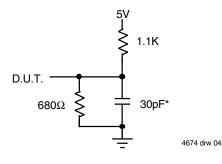

# AC TEST CONDITIONS

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 3ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| OutputLoad                    | See Figure 2 |

\* Includes jig and scope capacitances.

### Figure 2. Output Load

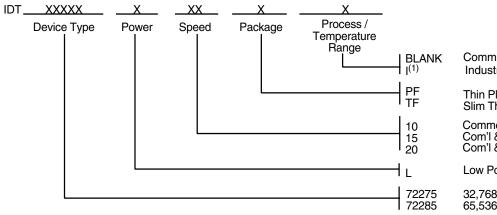

## **ORDERING INFORMATION**

Commercial (0 C to +70 C) Industrial (-40 C to +85 C)

Thin Plastic Quad Flatpack (TQFP, PN64-1) Slim Thin Quad Flatpack (STQFP, PP64-1)

Commercial Only Com'l & Ind'l Com'l & Ind'l Com'l & Ind'l

Low Power

32,768 x 18 SuperSyncFIFO 65,536 x 18 SuperSyncFIFO

4674 drw 24

### NOTE:

1. Industrial temperature range product for 15ns and 20ns speed grade are available as a standard device.